REACT

REACTive Environment for Runtime Reconfiguration - funded by DARPA

|

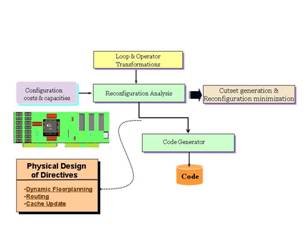

REACT program was funded under the DARPA Adaptive Computing Systems (ACS) efforts. A large scale hardware software co-execution based adaptive embedded computing system integrated the use of programmable technology for online reconfiguration and performance enhancement of large iterative computing applications. The software frontend is supported by a compiler that performs program analysis and architecture generation for hardware bound computations. The backend of the software performs dynamic floorplanning and routing for hardware bound computations and general purpose processor based code generation for software bound computations. An emulation based test and validation system aids the debugging task during application development and mapping cycle. REACT compiler has been tested over several ACS benchmarks and applications mapped to REACT environment have shown significant speedups over traditional software based executions.

RACE

Reconfigurable and Adaptive Computing Environment - funded by AFRL

|

RACE Board |

RACE program has resulted in two generations of reconfigurable hardware and associated software environments for mapping and executing designs on FPGA based hardware. RACE-I is a Xilinx 4000 family based SBUS compatible first generation architecture. The architecture has its own high speed SRAM based 512K memory and can implement upto 50K gate equivalent designs. RACE-I is supported by a well integrated tool suite that supports a utility to convert unannotated C to synthesizable VHDL, a system level partitioner, floorplanning and local routing tools. A library of kernel drivers facilitates easy hardware based execution of compute intense applications. A more recently completed dynamically and partially reconfigurable PCI bus based architecture called NEBULA has resulted in software directed hardware configuration approach.

|

NEBULA Board |

RACE and NEBULA have demonstrated the power of reconfigurable logic in many application areas. Extensions to RACE paradigm were recently demonstrated in a Jbits based application implementation medium which is suitable for rapid hardware development under the full control of software, internet based remote hardware configuration, and more.